Designing a fully differential two-stage op-amp and drawing the layout using Cadence

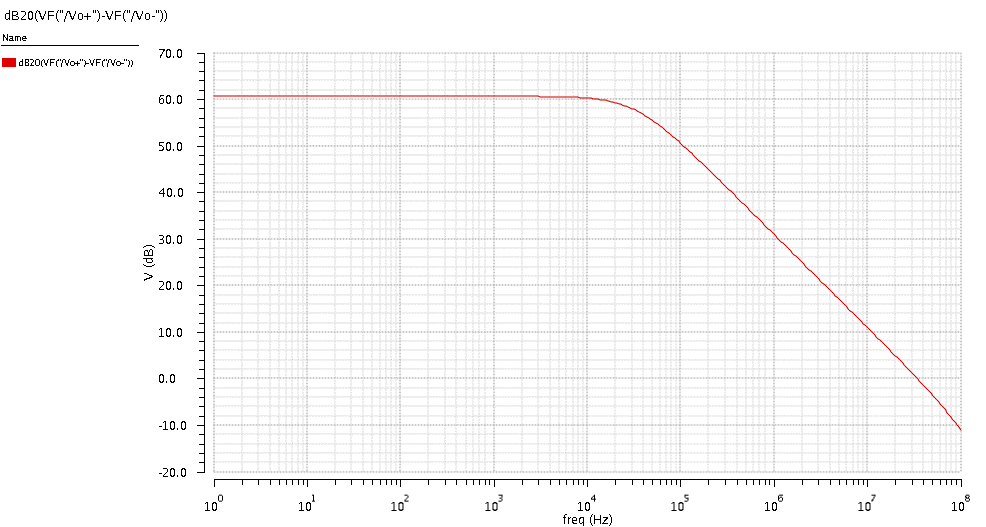

Using Cadence, I designed a fully differential two-stage op-amp with PMOS transistors as inputs in CMOS, 0.18μm technology, and drew the layout. The gain, slew rate, and phase margin are above 50 dB, 94 V/μSec, and 60°, respectively.

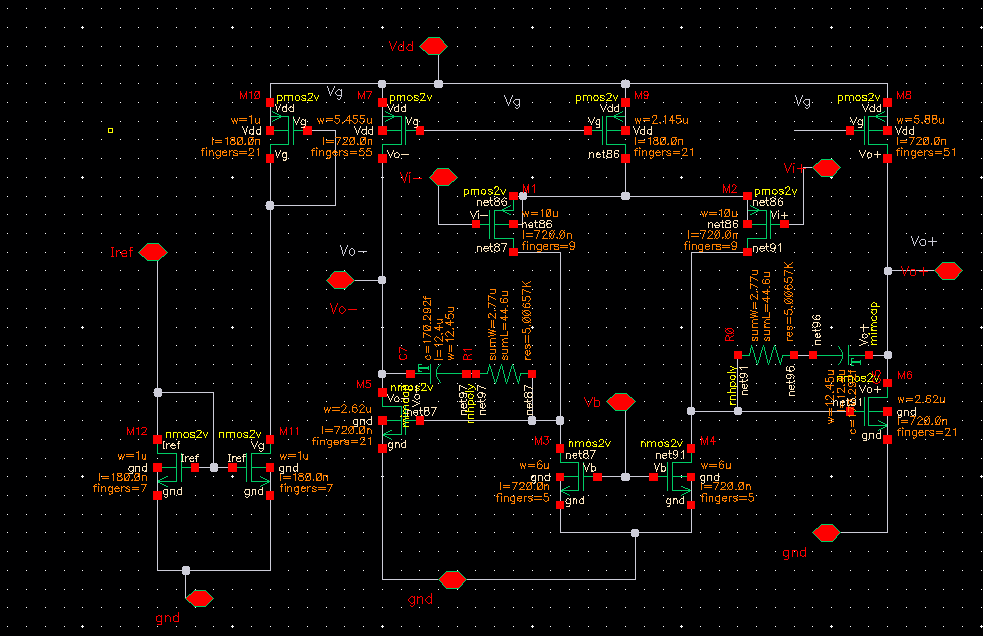

Circuit

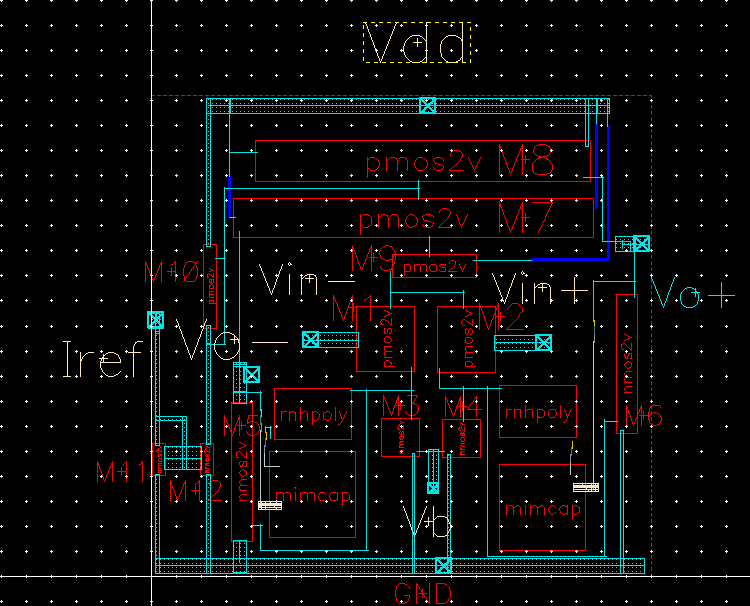

Layout

Output